- #Vivado download file failed to download software

- #Vivado download file failed to download series

- #Vivado download file failed to download simulator

- #Vivado download file failed to download windows

Running your simulation using scripts or makefiles means that you can easily add any prerequisite steps into your simulation flow, which allows you to keep everything consolidated in one place.įig.

#Vivado download file failed to download software

If you’re doing cosimulation with some C/C++ based software models, or compiling source code to create a binary for a CPU core you’re simulating, chances are you are using an external compiler like GCC, CLANG, or something more exotic. 3: Multiple `defines declared in some bash variables is much faster once you have a basic CLI flow set up - no more digging through various project setting menus just to find that one option you’re looking for.įig. Just like modifying the sources, customizing various parameters of Vivado CLI tools ( xvlog, xvhdl, xelab and xsim), adding plusargs, defines, etc. Quick parameter / configuration adjustment.2: Changing the source list is quick with any text editor Unlike the disaster that’s demonstrated in Figure 1, once you have your simulation flow and sources down in a bash script or a makefile, you can quickly modify said list with any text editor without having to use any sluggish GUI’s.įig. Quick and easy addition/removal of sources.In stark contrast, compiling, elaborating and simulating from the command line has some serious advantages: If you’ve used the Vivado GUI (and, I mean, surely you must have if you’re reading this) then you know how clunky the graphical interface is. 1: That's a lot of pixels just to add a source file Why bother? ⌗ In Part II, an example VHDL module is also included.įig.

Note: This guide uses SystemVerilog as the language of choice, but everything discussed here is applicable to VHDL and Verilog too. In Part I, we will get familiar with using the Vivado CLI tools.

#Vivado download file failed to download series

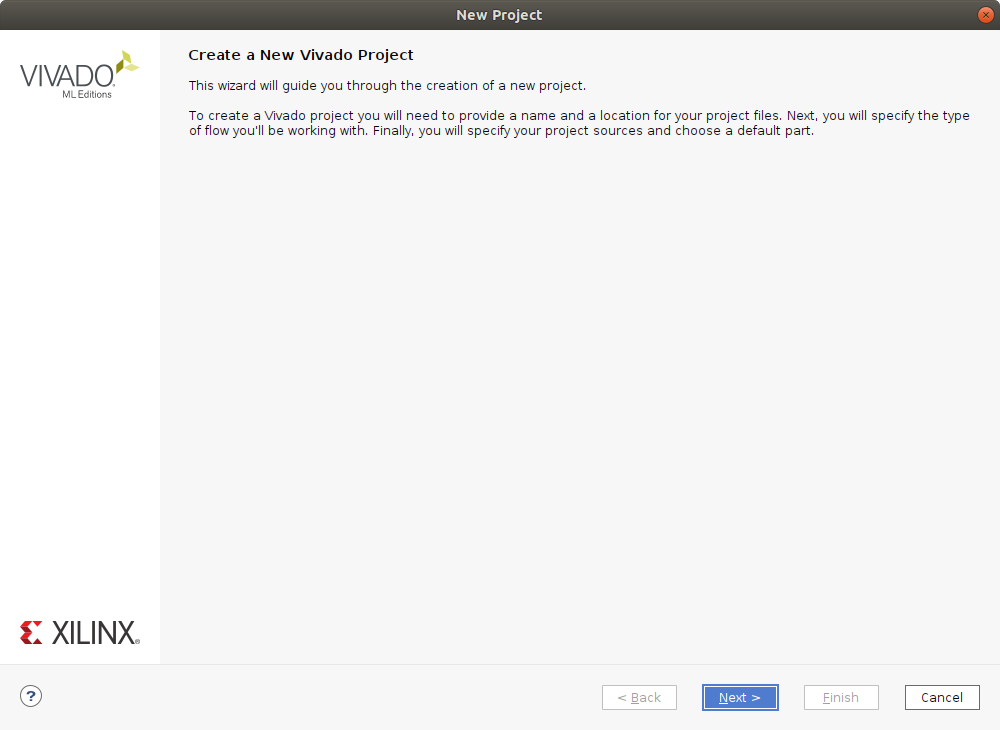

In the following series of guides, I will give you all the information you need to quickly move your simulation out of the graphical Vivado project into a scripted flow for easy compilation, elaboration, and simulation, all done using the Command Line Interface (CLI).

#Vivado download file failed to download windows

You probably feel that the interface is slow, and the number of windows and menus that must be navigated even for the most basic tasks is ridiculous. If you’re reading this post, you are likely frustrated with with the Xilinx Vivado GUI. Part IV - IP core and Block Design integration into scripted flow (coming soon).

#Vivado download file failed to download simulator

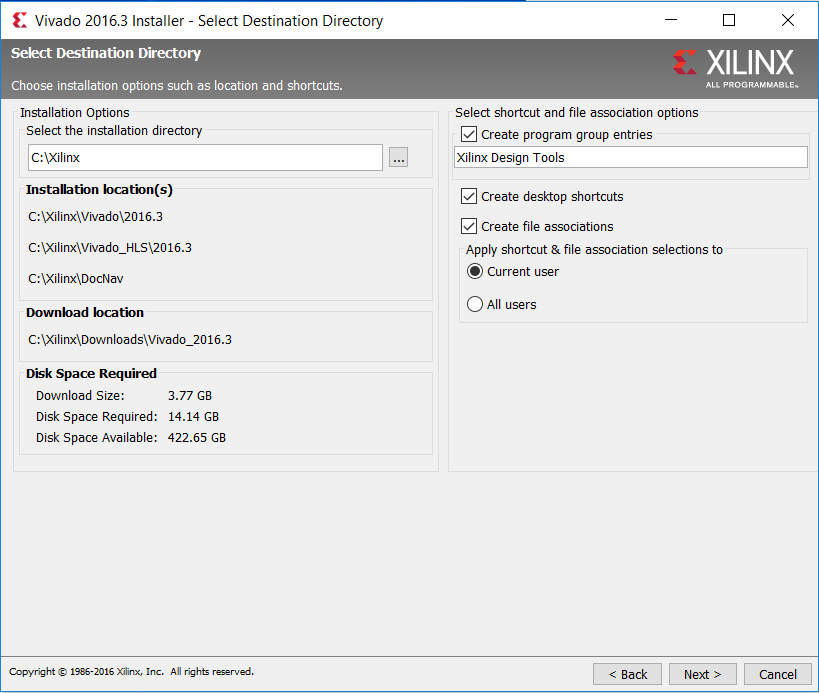

Part III - Vivado Simulator flow using Makefiles.Part II - Introduction to Bash scripting with Vivado tools.Make sure that all the files are pointing to the correct src/xxx/.vhd directory.Series on Vivado Simulator Scripted Flow (Bash, Makefiles) ⌗ Simulation files can be found at # Set 'sim_1' fileset object The same goes for simulation and constraints files.

Set_property -name "file_type" -value "VHDL" -objects $file_obj (This is where I failed in the initial question): set file "hdl/.vhd" With set origin_dir ]Īnd create_project $/src/hdl/.vhd"]\įuthermore, ach file needs a descriptive block like this, with a link to the directory where it is now.

0 kommentar(er)

0 kommentar(er)